FGM842D 硬件设计

简介

QuecOpen® 是一种以模块作为主处理器的解决方案。随着通信技术和市场的不断发展和演变,其优势日益凸显。它可以帮助您:

- 实现嵌入式应用的快速开发并缩短产品研发周期

- 简化电路和硬件结构设计以降低工程成本

- 使产品小型化

- 降低产品功耗

- 应用 OTA 技术

- 增强产品竞争力和成本效益

本文档定义了 QuecOpen® 解决方案中的 FGM842D 系列,并描述了其空中接口和硬件接口,这些接口与您的应用相连。本文档提供了对模块接口规格、RF 性能、电气和机械规格以及其他相关信息的快速洞察。

为简洁起见,FGM842D 和 FGM842D-P 在本文档中适用于两款型号的部分中统称为“模块/模块”,而在仅指两款型号差异的部分中分别称为“FGM842D”和“FGM842D-P”。

特殊标记

特殊标记:

| 标记 | 定义 |

|---|---|

| […] | 括号 ([…]) 用于引脚后括起数字范围表示相同类型的引脚。例如,SDIO_DATA[0:3] 指所有四个 SDIO 引脚:SDIO_DATA0、SDIO_DATA1、SDIO_DATA2 和 SDIO_DATA3。 |

产品概述

FGM842D 系列是高性能 MCU Wi-Fi 4 和蓝牙模块,支持 IEEE 802.11b/g/n 和 BLE 5.2 协议。它提供多种接口,包括 UART、GPIO、SPI、I2C、PWM 和 ADC,用于各种应用。

它是一个 SMD 模块,具有紧凑的封装。包括:

- 160 MHz MCU 处理器

- 内置 288 KB RAM 和 2 MB Flash

- 支持二次开发

基本信息:

| FGM842D 系列 | 描述 |

|---|---|

| 封装类型 | LGA |

| 引脚数量 | 61 |

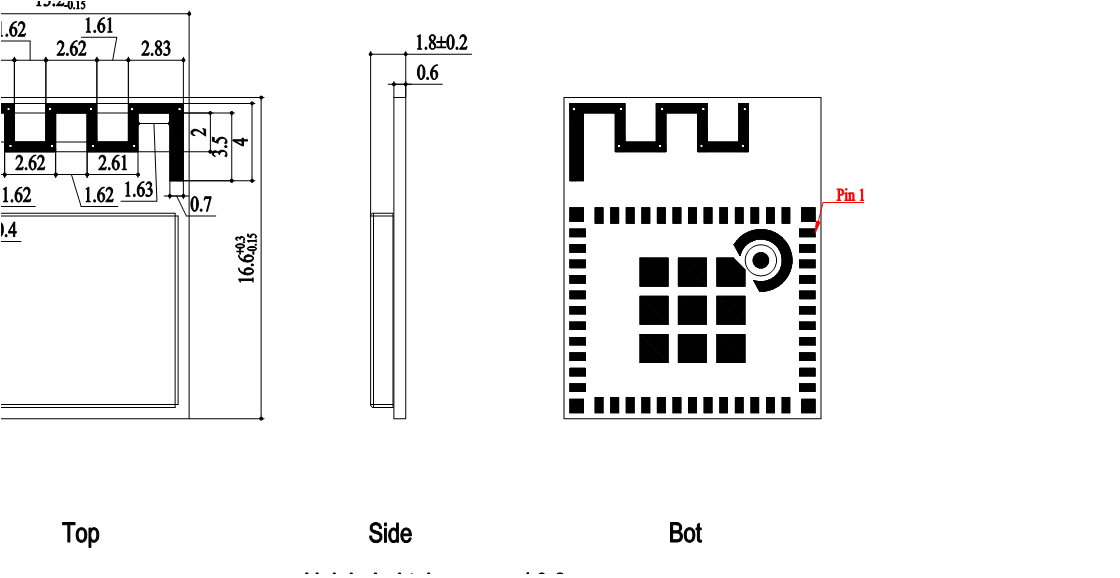

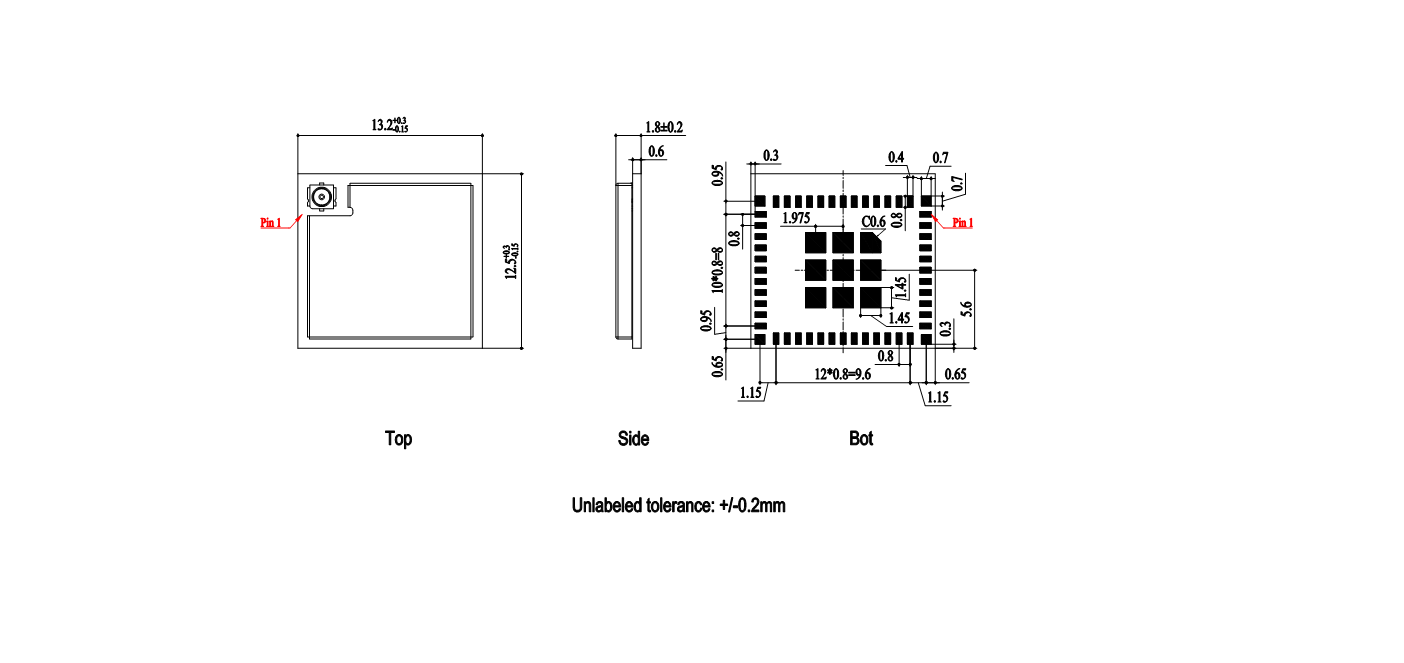

| 尺寸 | FGM842D: (12.5 +0.3/-0.15) mm × (13.2 +0.3/-0.15) mm × (1.8 ±0.2) mm FGM842D-P: (16.6 +0.3/-0.15) mm × (13.2 +0.3/-0.15) mm × (1.8 ±0.2) mm |

| 重量 | FGM842D: 约 1.05 g FGM842D-P: 约 1.14 g |

| 型号 | FGM842D, FGM842D-P |

关键特性

关键特性:

| 基本信息 | 描述 |

|---|---|

| 协议和标准 | Wi-Fi 协议:IEEE 802.11b/g/n 蓝牙协议:BLE 5.2 所有硬件组件完全符合欧盟 RoHS 指令 |

| 电源供应 | VBAT 电源供应: 3.0–3.6 V 典型:3.3 V |

| 温度范围 1 | 设计方案1: 正常工作温度:-40 °C 至 +105 °C 存储温度:-45 °C 至 +115 °C 设计方案2: 正常工作温度:-40 °C 至 +105 °C 存储温度:-45 °C 至 +115 °C |

| TE-B 套件 | FGM842D-TE-B 2 |

| 天线/天线接口 | |

| 天线/天线接口 | FGM842D3:引脚天线接口 (ANT_WIFI/BT) 或 RF 同轴连接器 FGM842D-P:PCB 天线 50 Ω 特性阻抗 |

| 应用接口4 | |

| 应用接口 | UART, GPIO, SPI, I2C PWM, ADC |

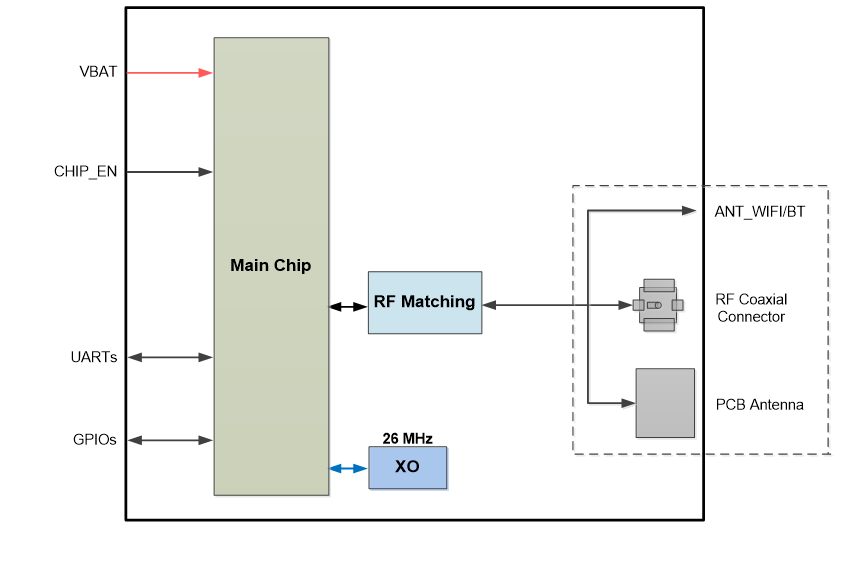

功能图

下图显示了模块的功能框图,并说明了主要功能部件。

应用接口

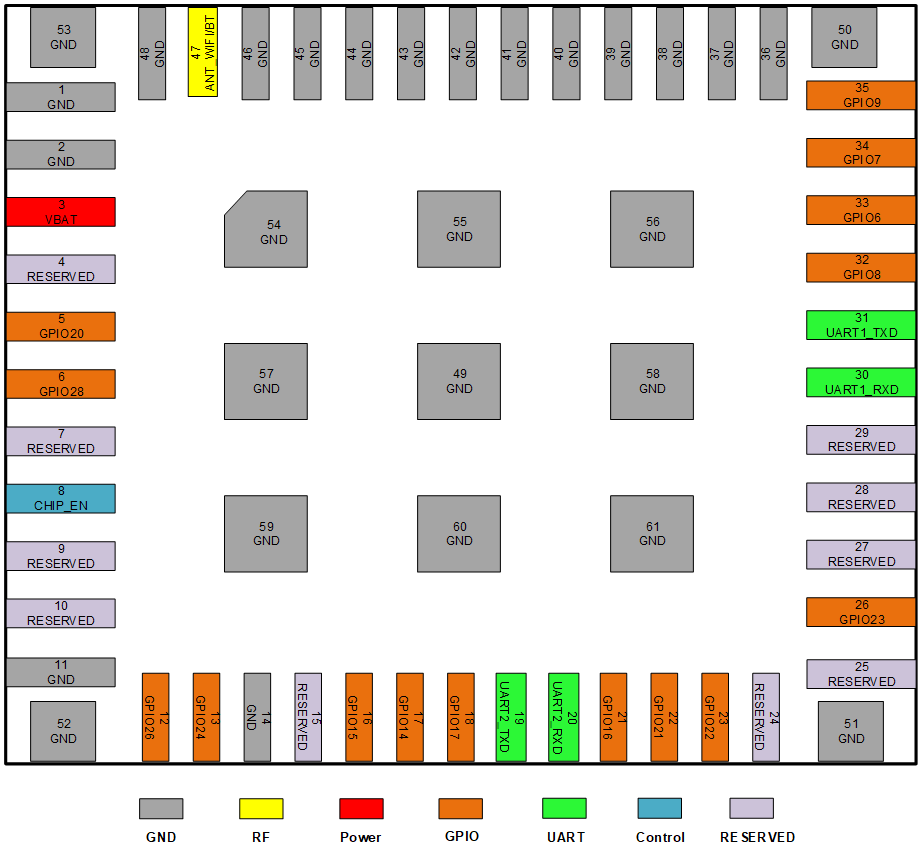

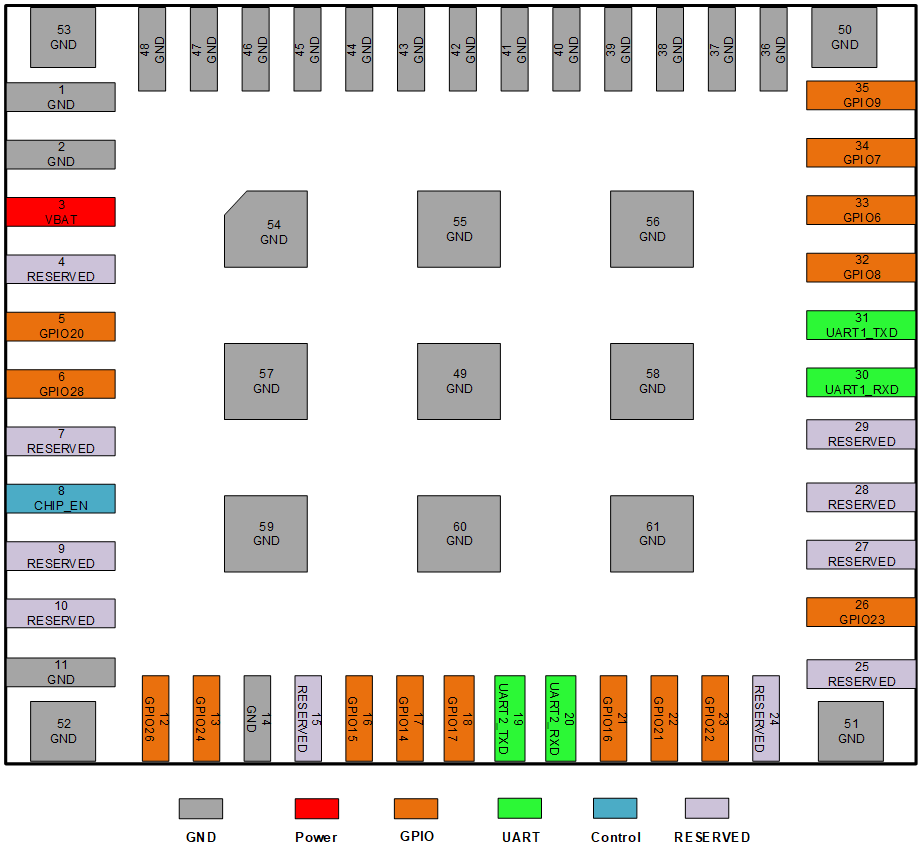

引脚分配

引脚描述

参数描述:

| 参数 | 描述 |

|---|---|

| AIO | 模拟输入/输出 |

| DI | 数字输入 |

| DO | 数字输出 |

| DIO | 数字输入/输出 |

| PI | 电源输入 |

DC 特性包括电源域和额定电流。

引脚描述:

电源供应和 GND 引脚:

| 引脚名称 | 引脚编号 | I/O | 描述 | DC 特性 | 注释 |

|---|---|---|---|---|---|

| VBAT | 3 | PI | 模块电源供应 | Vmax = 3.6V Vmin = 3.0V Vnom = 3.3V |

建议提供至少 0.6A 的电流。 |

| GND | FGM842D: 1, 2, 11, 14, 36-46,48-61 FGM842D-P: 1, 2, 11, 14, 36-61 |

- | - | - | - |

控制信号:

| 引脚名称 | 引脚编号 | I/O | 描述 | DC 特性 | 注释 |

|---|---|---|---|---|---|

| CHIP_EN | 8 | DI | 启用模块 | VBAT | 硬件启用。内部上拉至 3.3 V。主动高。 |

UART 接口:

| 引脚名称 | 引脚编号 | I/O | 描述 | DC 特性 | 注释 |

|---|---|---|---|---|---|

| UART1_TXD | 31 | DO | UART1 发送 | VBAT | - |

| UART1_RXD | 30 | DI | UART1 接收 | VBAT | - |

| UART2_TXD | 19 | DO | UART2 发送 | VBAT | - |

| UART2_RXD | 20 | DI | UART2 接收 | VBAT | - |

GPIO 接口:

| 引脚名称 | 引脚编号 | I/O | 描述 | DC 特性 | 注释 |

|---|---|---|---|---|---|

| GPIO20 | 5 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO28 | 6 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO26 | 12 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO24 | 13 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO15 | 16 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO14 | 17 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO17 | 18 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO16 | 21 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO21 | 22 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO22 | 23 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO23 | 26 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO8 | 32 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO6 | 33 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO7 | 34 | DIO | 通用输入/输出 | VBAT | 唤醒 |

| GPIO9 | 35 | DIO | 通用输入/输出 | VBAT | 唤醒 |

FGM842D RF 天线接口:

| 引脚名称 | 引脚编号 | I/O | 描述 | DC 特性 | 注释 |

|---|---|---|---|---|---|

| ANT_WIFI/BT | 47 | AIO | WiFi/蓝牙 | - | 50Ω 特性 |

RESERVED 引脚:

| 引脚名称 | 引脚编号 | 注释 |

|---|---|---|

| RESERVED | 4, 7, 9, 10, 15, 24, 25, 27-29 | 保持开路 |

GPIO 多路复用

模块默认提供 15 个 GPIO 接口,在多路复用情况下,可以支持最多 19 个 GPIO 接口。引脚定义如下:

GPIO 多路复用:

| 引脚名称 | 引脚编号 | 备用功能 0 (GPIO 编号) | 备用功能 1 | 备用功能 2 | 备用功能 3 | 备用功能 4 |

|---|---|---|---|---|---|---|

| GPIO14 | 17 | GPIO14 | SPI_CLK | - | - | - |

| GPIO17 | 18 | GPIO17 | SPI_MISO | I2C_SDA | - | - |

| GPIO16 | 21 | GPIO16 | SPI_MOSI | - | - | - |

| GPIO15 | 16 | GPIO15 | SPI_CS | I2C_SCL | - | - |

| UART2_TXD | 19 | GPIO0 | - | - | - | - |

| UART2_RXD | 20 | GPIO1 | ADC5 | - | - | - |

| GPIO23 | 26 | GPIO23 | - | - | - | - |

| GPIO6 | 33 | GPIO6 | CLK13M | PWM0 | JTAG_TCK | - |

| GPIO7 | 34 | GPIO7 | PWM1 | JTAG_TMS | - | - |

| GPIO8 | 32 | GPIO8 | PWM2 | JTAG_TDI | CLK26M | - |

| GPIO9 | 35 | GPIO9 | PWM3 | JTAG_TDO | - | - |

| GPIO21 | 22 | GPIO21 | - | - | - | - |

| UART1_RXD | 30 | GPIO10 | ADC6 | - | - | - |

| UART1_TXD | 31 | GPIO11 | - | - | - | - |

| GPIO22 | 23 | GPIO22 | - | - | - | - |

| GPIO28 | 6 | GPIO28 | ADC4 | - | - | - |

| GPIO20 | 5 | GPIO20 | ADC3 | - | - | - |

| GPIO24 | 13 | GPIO24 | LPO_CLK | PWM4 | I2C_SCL | ADC2 |

| GPIO26 | 12 | GPIO26 | PWM5 | I2C_SDA | ADC1 | - |

- 所有 GPIO 均可作为休眠中断使用,在唤醒后模块可以立刻进入工作状态。

- 通过 GPIO 复用来的各应用接口最大数量不可同时实现。对于模块可支持各应用接口最大数量,详情可参考接口详情。

接口详情

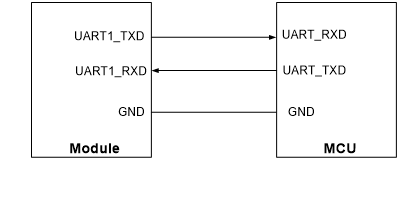

UART 接口

模块默认提供 2 个 UART 接口,所有接口都可以支持全双工异步串行通信,波特率高达 6 Mbps。

UART 接口引脚定义:

| 引脚名称 | 引脚编号 | I/O | 描述 |

|---|---|---|---|

| UART1_TXD | 31 | DO | UART1 发送 |

| UART1_RXD | 30 | DI | UART1 接收 |

| UART2_TXD | 19 | DO | UART2 发送 |

| UART2_RXD | 20 | DI | UART2 接收 |

UART1 可用于下载、数据传输和 AT 命令通信,默认波特率为 115200 bps。模块与 MCU 的 UART1 连接如下所示。

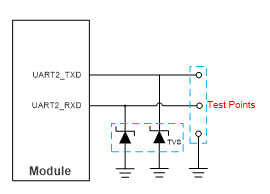

UART2 可作为调试 UART,用于输出部分日志,默认波特率为 921600 bps。UART2 的参考设计如下。

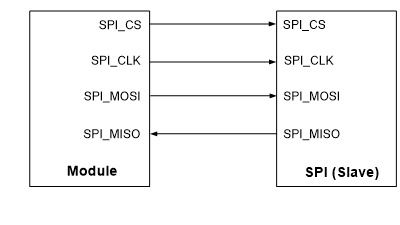

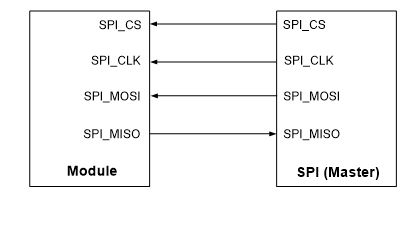

SPI

在多路复用情况下,模块提供一个 SPI,支持主从模式。接口的最大时钟频率在从模式下可达 20 MHz,在主模式下可达 30 MHz。

SPI 引脚定义:

| 引脚名称 | 引脚编号 | 备用功能 | I/O | 描述 | 注释 |

|---|---|---|---|---|---|

| GPIO15 | 16 | SPI_CS | DIO | SPI 芯片选择 | 在主模式下,它是一个输出信号;在从模式下,它是一个输入信号。 |

| GPIO14 | 17 | SPI_CLK | DIO | SPI 时钟 | 在主模式下,它是一个输出信号;在从模式下,它是一个输入信号。 |

| GPIO17 | 18 | SPI_MISO | DIO | SPI 主入从出 | - |

| GPIO16 | 21 | SPI_MOSI | DIO | SPI 主出从入 | - |

以下图显示了主机与模块之间的 SPI 连接:

I2C 接口

在多路复用情况下,模块提供两个 I2C 接口,支持主从模式。接口支持标准(高达 100 kbps)和快速(高达 400 kbps)模式,具有 7 位寻址。

I2C 接口引脚定义:

| 引脚名称 | 引脚编号 | 备用功能 | I/O | 描述 |

|---|---|---|---|---|

| GPIO17 | 18 | I2C_SDA | OD | I2C 串行数据 |

| GPIO15 | 16 | I2C_SCL | OD | I2C 串行时钟 |

| GPIO24 | 13 | I2C_SCL | OD | I2C 串行时钟 |

| GPIO26 | 12 | I2C_SDA | OD | I2C 串行数据 |

当 I2C 接口连接到外部设备时,保留 1–10 kΩ 上拉电阻至 VBAT。

PWM 接口

在多路复用情况下,模块支持最多六个 32 位 PWM 接口。

PWM 接口引脚定义:

| 引脚名称 | 引脚编号 | 备用功能 | I/O | 描述 |

|---|---|---|---|---|

| GPIO6 | 33 | PWM0 | DO | PWM0 输出 |

| GPIO7 | 34 | PWM1 | DO | PWM1 输出 |

| GPIO8 | 32 | PWM2 | DO | PWM2 输出 |

| GPIO9 | 35 | PWM3 | DO | PWM3 输出 |

| GPIO24 | 13 | PWM4 | DO | PWM4 输出 |

| GPIO26 | 12 | PWM5 | DO | PWM5 输出 |

ADC 接口

在多路复用情况下,模块支持最多六个 10 位 ADC 接口,其输入电压范围为 0–3.3 V。为了提高 ADC 精度,在 ADC 走线周围放置接地。

ADC 接口引脚定义:

| 引脚名称 | 引脚编号 | 备用功能 | I/O | 描述 |

|---|---|---|---|---|

| UART2_RXD | 20 | ADC5 | AI | 通用 ADC 接口 |

| UART1_RXD | 30 | ADC6 | AI | 通用 ADC 接口 |

| GPIO28 | 6 | ADC4 | AI | 通用 ADC 接口 |

| GPIO20 | 5 | ADC3 | AI | 通用 ADC 接口 |

| GPIO24 | 13 | ADC2 | AI | 通用 ADC 接口 |

| GPIO26 | 12 | ADC1 | AI | 通用 ADC 接口 |

ADC 特性:

| 参数 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| ADC 输入电压范围 | 0 | - | 3.3 | V |

| ADC 分辨率 | - | 10 | - | bit |

操作特性

电源供应

模块的电源供应引脚和接地引脚定义在下表中。

电源供应和 GND 引脚引脚定义:

| 引脚名称 | 引脚编号 | I/O | 描述 | 最小值 | 典型值 | 最大值 | 单位 | |

|---|---|---|---|---|---|---|---|---|

| VBAT | 3 | PI | 模块电源供应 | 3.0 | 3.3 | 3.6 | V | |

| GND | GND: FGM842D: 1, 2, 11, 14, 36-46,48-61; FGM842D-P: 1, 2, 11, 14, 36-61 |

|||||||

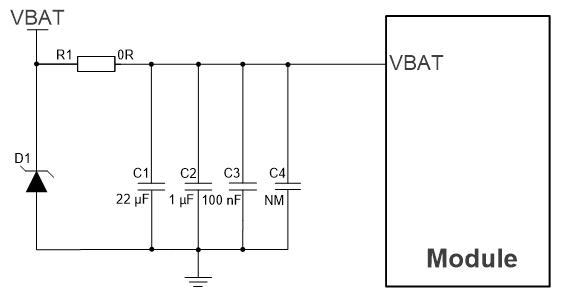

电源供应参考设计

模块由 VBAT 供电,建议使用能够提供至少 0.6 A 电流的电源芯片。为了获得更好的电源性能,建议在模块的 VBAT 引脚附近并联一个 22 μF 去耦电容,以及两个滤波电容(1 μF 和 100 nF)。C4 为调试保留,默认不安装。此外,建议在 VBAT 附近添加一个 TVS 以提高模块的浪涌电压承受能力。原则上,VBAT 走线越长,应越宽。

VBAT 参考电路如下所示:

开机

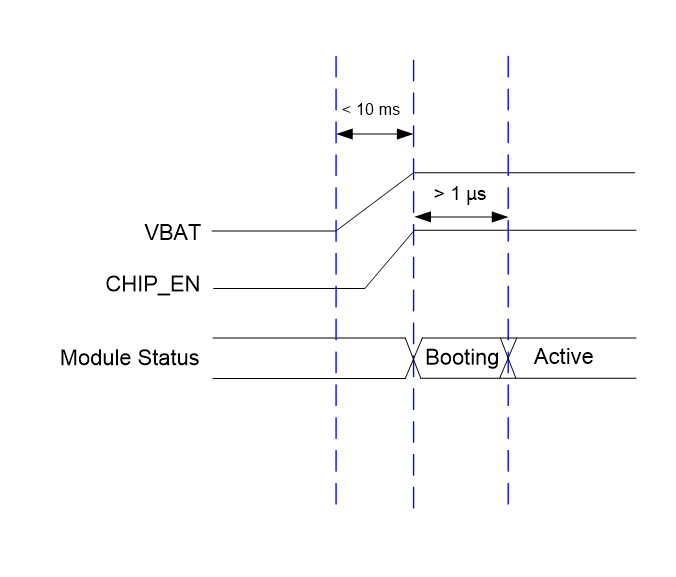

模块 VBAT 上电后,保持 CHIP_EN 为高电平以实现模块的自动启动。

CHIP_EN 引脚定义:

| 引脚名称 | 引脚编号 | I/O | 描述 | 注释 |

|---|---|---|---|---|

| CHIP_EN | 8 | DI | 模块使能 | 硬件使能; 内部上拉至 3.3 V; 高电平有效。 |

开机时序如下所示:

重置

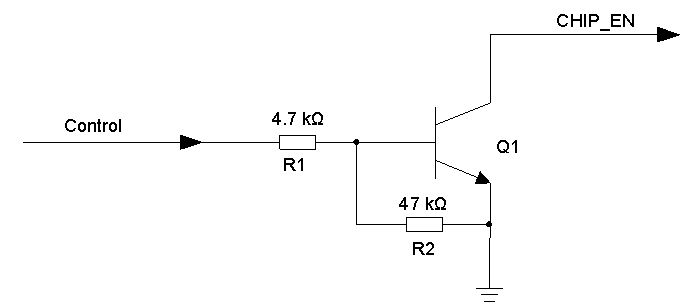

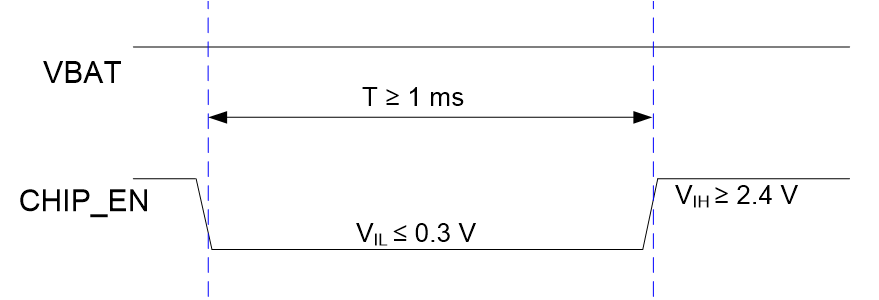

当 CHIP_EN 下降到 0.3 V 以下或将 CHIP_EN 下拉至少 1 ms 时,可以重置模块。模块硬件重置的参考设计如下所示。可以使用开集驱动电路来控制 CHIP_EN 引脚。

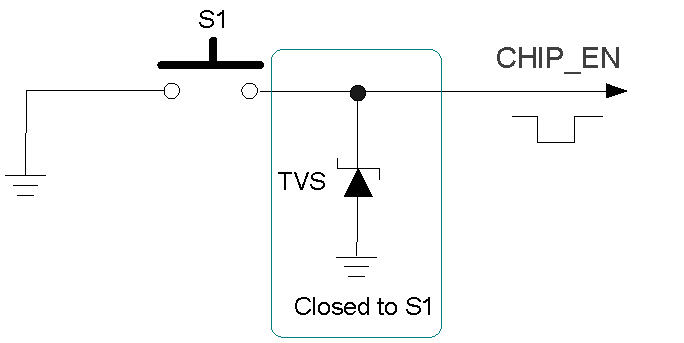

控制 CHIP_EN 的另一种方式是直接使用按钮。当按下按钮时,手指可能产生静电放电。因此,应在按钮附近放置一个 TVS 组件以进行 ESD 保护。

模块重置时序如下图所示。

RF 性能

Wi-Fi 性能

| 工作频率 | ||||

|---|---|---|---|---|

| 2.4 GHz: 2.400–2.4835 GHz | ||||

| 调制 | ||||

| DBPSK, DQPSK, CCK, BPSK, QPSK, 16QAM, 64QAM | ||||

| 工作模式 | ||||

|

||||

| 加密模式 | ||||

| WPA-PSK, WPA2-PSK, WPA3-SAE, AES-128, TRNG | ||||

| 数据传输速率 | ||||

|

||||

| 条件 (VBAT = 3.3 V; 温度:25 °C) | EVM | 典型值;单位:dBm,容差:±2 dB | ||

| 发射功率 | 接收灵敏度 | |||

| 2.4 GHz | 802.11b @ 1 Mbps | ≤ 35 % | 18 | -98 |

| 802.11b @ 11 Mbps | 18 | -90 | ||

| 802.11g @ 6 Mbps | ≤ -5 dB | 16 | -90 | |

| 802.11g @ 54 Mbps | ≤ -25 dB | 15 | -76 | |

| 802.11n, HT20 @ MCS 0 | ≤ -5 dB | 15 | -90 | |

| 802.11n, HT20 @ MCS 7 | ≤ -27 dB | 14 | -72 | |

蓝牙性能

| 工作频率 | ||

|---|---|---|

| 2.400–2.4835 GHz | ||

| 调制 | ||

| GFSK | ||

| 工作模式 | ||

| BLE | ||

| 条件 (VBAT = 3.3 V; 温度:25 °C) | 典型值;单位:dBm,容差:±2 dB | |

| 发射功率 | 接收灵敏度 | |

| BLE (1 Mbps) | 6 | -96 |

| BLE (2 Mbps) | 6 | -94 |

| BLE (S = 2) | 6 | -96 |

| BLE (S = 8) | 6 | -101 |

天线/天线接口

FGM842D 提供两种天线接口设计之一:引脚天线接口 (ANT_WIFI/BT) 或 RF 同轴连接器。当模块设计为 ANT_WIFI/BT 天线接口时,RF 同轴连接器不可用;FGM842D-P 支持 PCB 天线。天线端口的阻抗为 50 Ω。

应根据特定应用使用适当的天线类型和设计,并匹配天线参数。在大规模生产终端产品之前,需要进行全面的功能测试。本章的所有内容仅供说明,在设计目标产品时,仍需要进行分析、评估和确定。

FGM842D 引脚天线接口 (ANT_WIFI/BT) 5

ANT_WIFI/BT 引脚定义:

| 引脚名称 | 引脚编号 | I/O | 描述 | 注释 |

|---|---|---|---|---|

| ANT_WIFI/BT | 47 | AIO | Wi-Fi/蓝牙天线接口 | 50 Ω 特性阻抗。 |

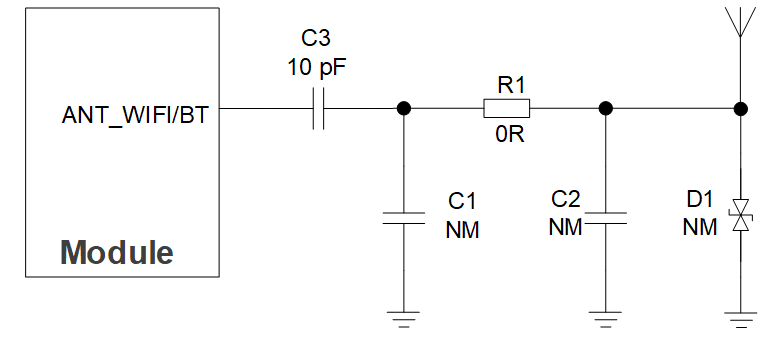

参考设计

下图为射频天线接口的电路。为了达到更佳的射频性能,需预留 π 型匹配电路和 ESD 防护器件。预留匹配元件如 R1、C1、C2,D1 应尽量靠近天线放置,R1 推荐值为 0 Ω,TVS 寄生电容小于 0.05 pF,C1、C2、D1 默认不贴。

天线设计要求

天线设计要求:

| 类型 | 要求 |

|---|---|

| 频率范围(GHz) | 2.400–2.4835 |

| 插损(dB) | < 1 |

| VSWR | ≤ 2(典型值) |

| 增益(dBi) | 1(典型值) |

| 最大输入功率(W) | 50 |

| 输入阻抗(Ω) | 50 |

| 极化类型 | 垂直 |

射频信号线布线指导

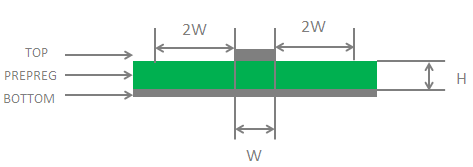

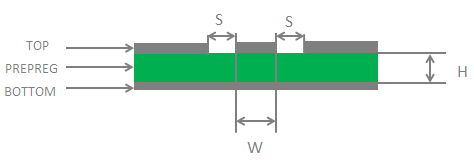

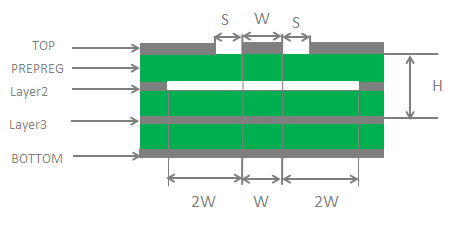

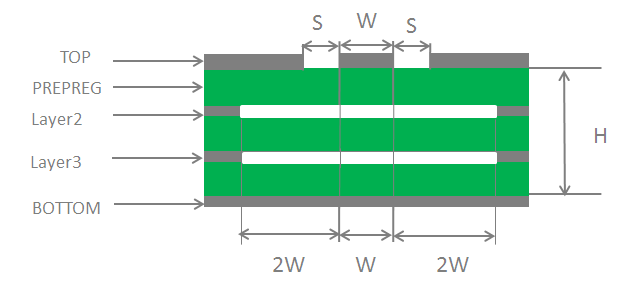

设计 PCB 时,所有射频信号线的特性阻抗应控制在 50 Ω。一般情况下,射频信号线的阻抗由材料的介电常数、走线宽度(W)、对地间隙(S)、以及参考地平面的高度(H)决定。PCB 特性阻抗的控制通常采用微带线与共面波导两种方式。为了体现设计原则,下面几幅图展示了阻抗线控制在 50 Ω 时,微带线以及共面波导的结构设计。

为了确保 RF 性能和可靠性,在 RF 布局设计中遵循以下原则:

- 使用阻抗模拟工具准确控制 RF 走线的特性阻抗为 50 Ω。

- 相邻 RF 引脚的 GND 引脚不应设计为热释垫,并应完全连接到地。

- RF 引脚与 RF 连接器的距离应尽可能短,所有直角走线应更改为曲线。推荐走线角度为 135°。

- 天线连接器或焊盘的信号引脚下方应有间隙。

- RF 走线的参考地应完整。同时,在 RF 走线周围添加一些接地过孔可以帮助改善 RF 性能。接地过孔与 RF 走线的距离应至少为 RF 信号走线宽度的两倍 (2 × W)。

- 将 RF 走线远离干扰源(如 DC-DC、(U)SIM/USB/SDIO 高频数字信号、显示信号和时钟信号),并避免相邻层之间的交叉和并行。

有关 RF 布局的更多详细信息,请参见 RF-Layout-Application-Note。

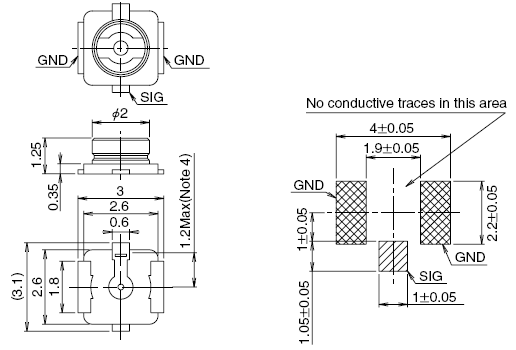

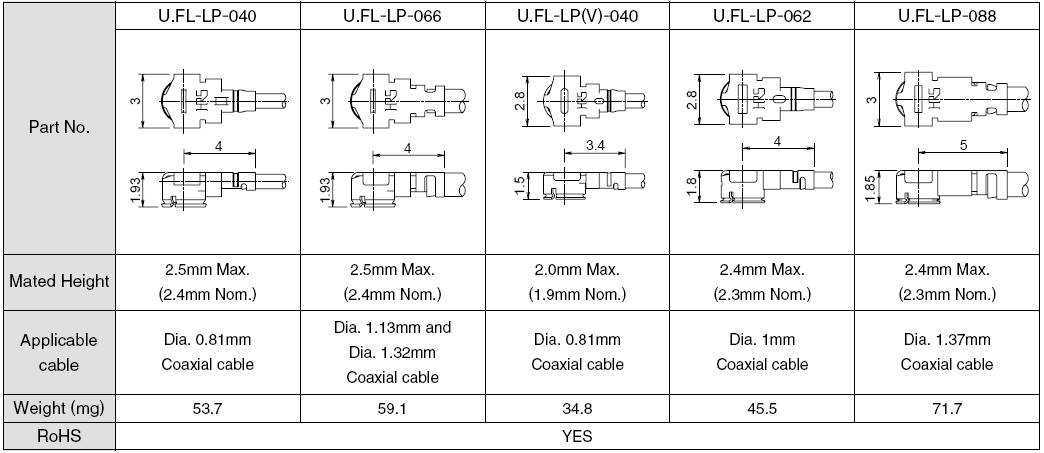

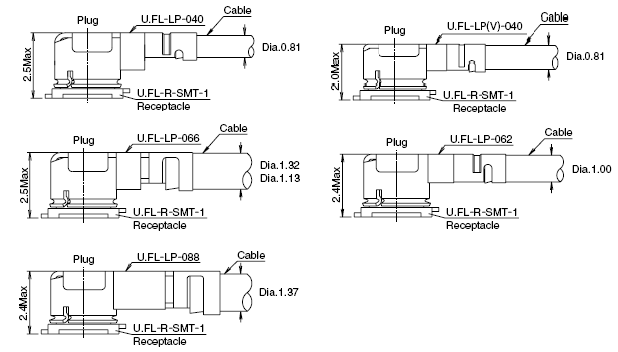

如果使用 RF 连接器进行天线连接,推荐使用 Hirose 提供的 U.FL-R-SMT 连接器。

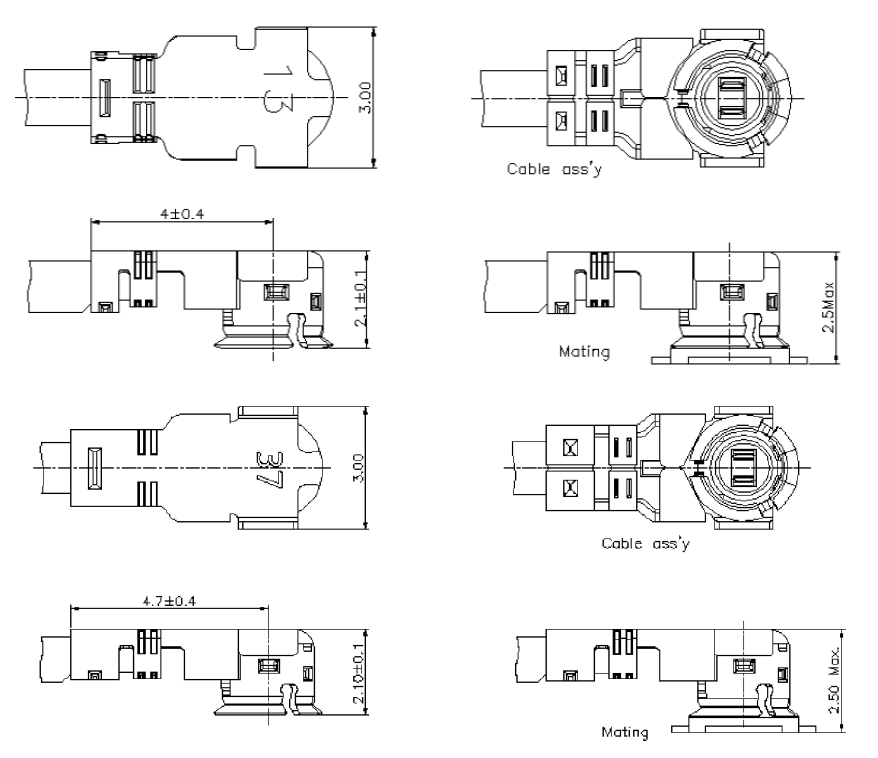

以下图中列出的 U.FL-LP 系列配套插头可与 U.FL-R-SMT 连接器匹配。

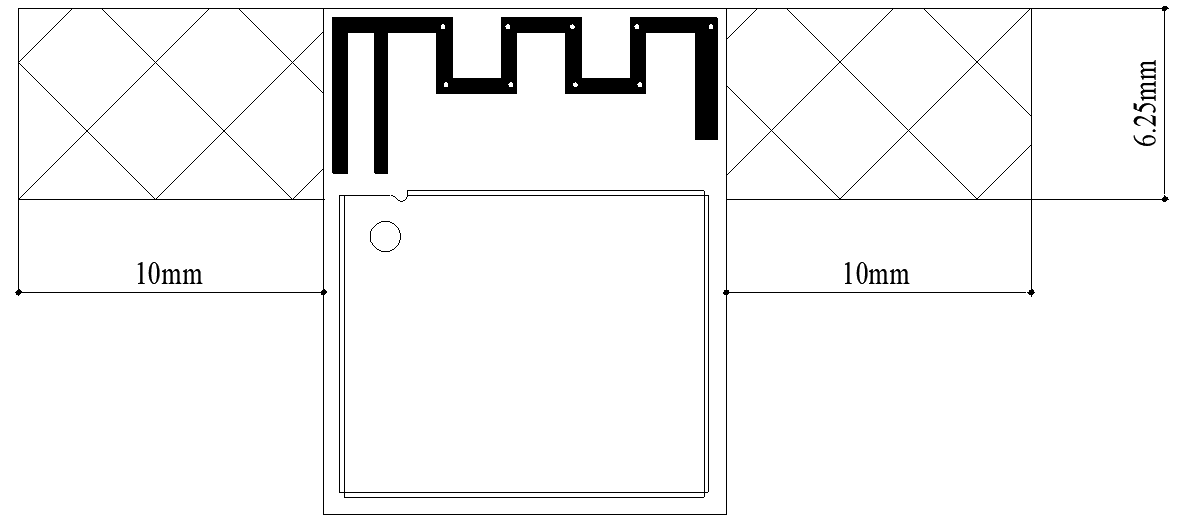

以下图描述了配套连接器的空间因子。

有关更多详细信息,请访问 http://www.hirose.com。

FGM842D RF 同轴连接器 6

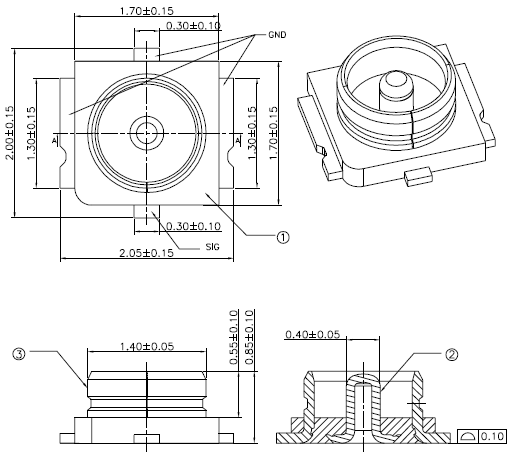

天线座规格

模块支持的接收器机械尺寸如下。

RF 连接器的主要规格:

| 参数 | 规格 |

|---|---|

| 标称频率范围 | DC 至 6 GHz |

| 标称阻抗 | 50 Ω |

| 温度额定值 | -40 °C 至 +105 °C |

| 电压驻波比 (VSWR) | 符合以下要求: 最大 1.3 (DC–3 GHz) 最大 1.45 (3–6 GHz) |

天线连接器安装

以下图中列出的配套插头可与连接器匹配。

推荐 RF 连接器安装

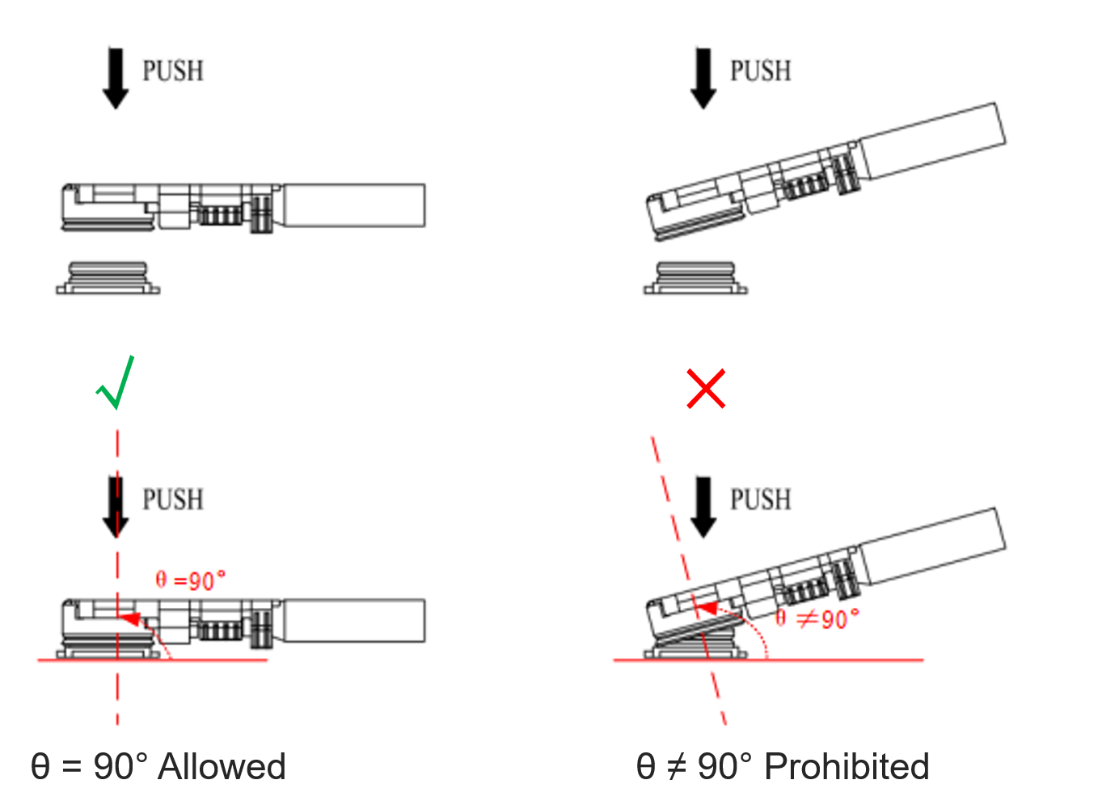

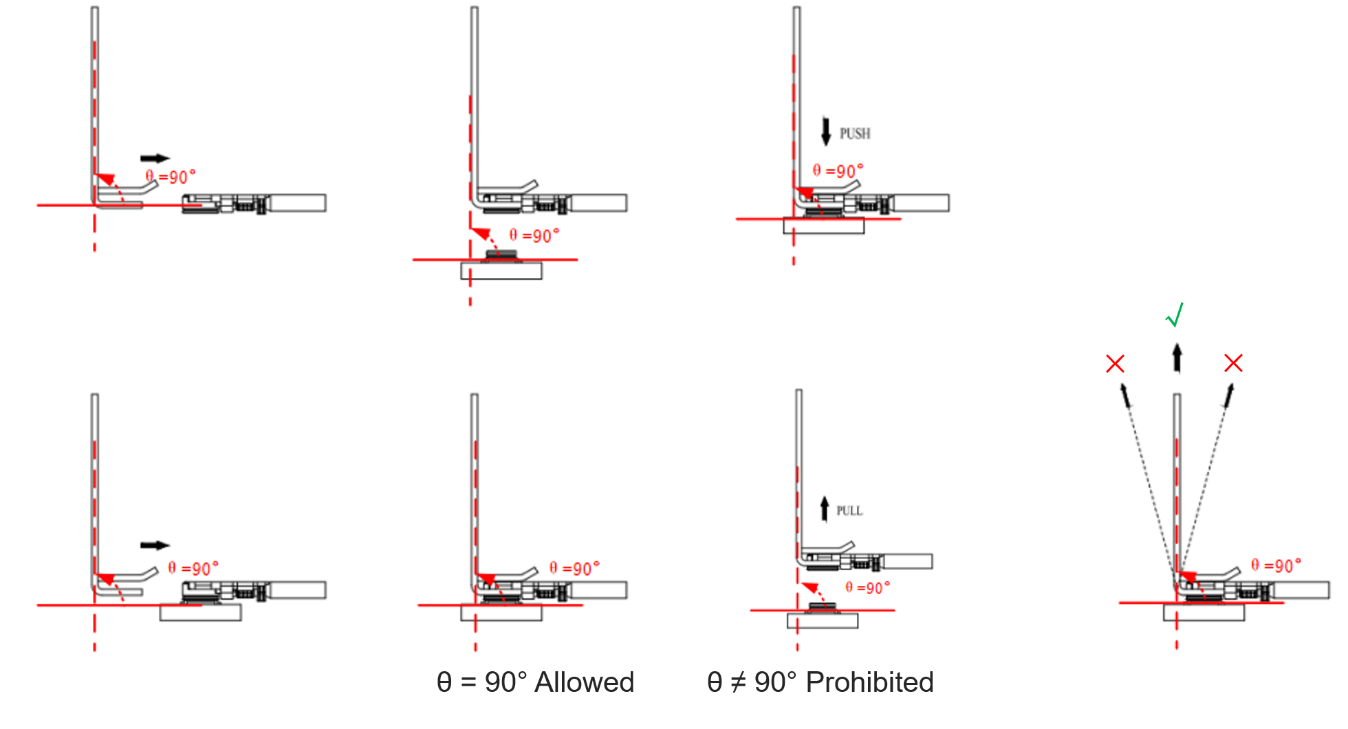

以下图片显示了插入同轴电缆插头的过程,θ = 90° 是可接受的,而 θ ≠ 90° 则不可接受。

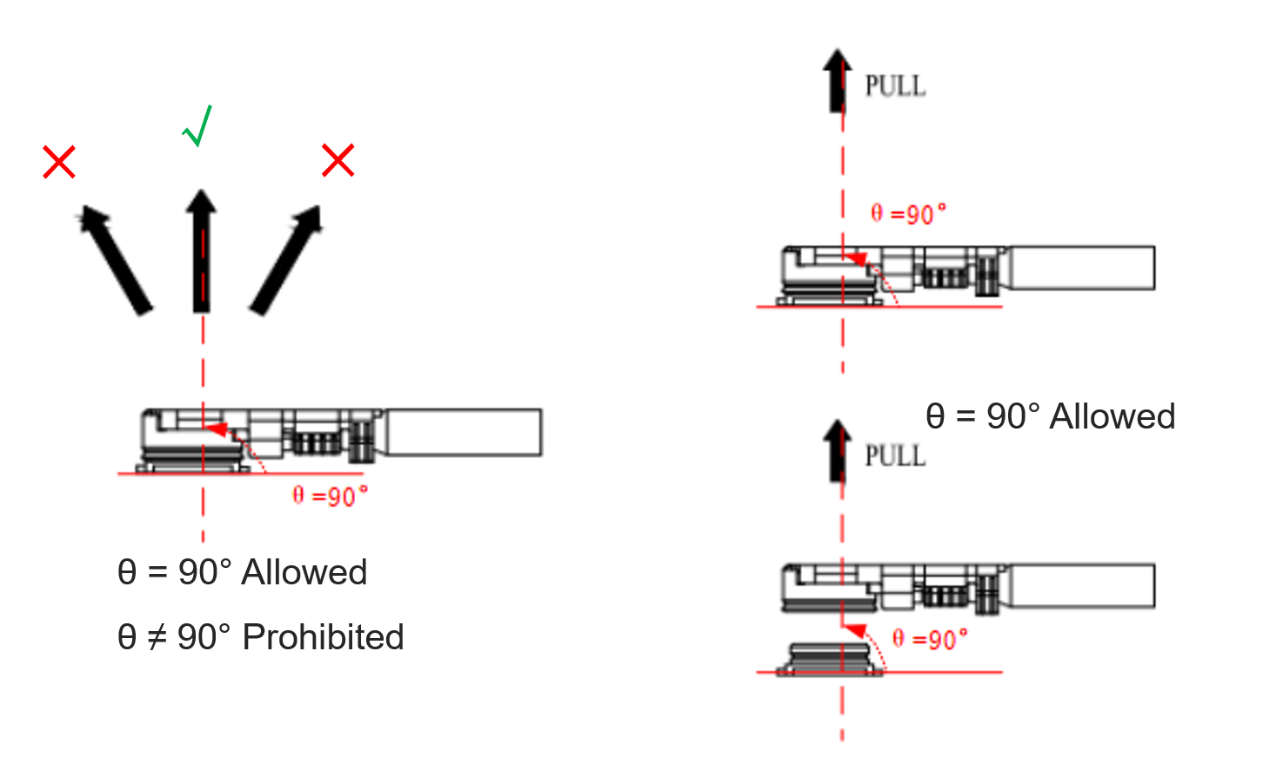

以下图片显示了拔出同轴电缆插头的过程,θ = 90° 是可接受的,而 θ ≠ 90° 则不可接受。

以下图片显示了使用夹具安装同轴电缆插头的过程,θ = 90° 是可接受的,而 θ ≠ 90° 则不可接受。

推荐 RF 连接器和电缆制造商

推荐使用 I-PEX 的 RF 连接器和电缆。有关更多详细信息,请访问 https://www.i-pex.com。

FGM842D-P PCB 天线

PCB 天线的性能取决于整个产品,包括主板、外壳和其他 RF 信号,并建议在设计早期进行验证。为了在使用 PCB 天线设计时确保性能和可靠性,请遵循以下基本原则进行模块放置和布局:

- 模块应放置在主板的边缘。

- 在主板上,所有 PCB 天线下方的 PCB 层应设计为禁止布线区域。

- 在主板上,确保 PCB 天线与过孔、走线、铜箔区域和其他组件(如连接器、以太网端口和任何金属组件)之间至少有 16 毫米的间隙。

- 如果使用塑料外壳,确保 PCB 天线与塑料外壳之间至少有 10 毫米的间隙。如果使用金属外壳,建议使用外部天线。

如果无法保证上述任何原则,建议探索模块的替代天线解决方案或寻求移远通信天线团队的帮助,他们可以提供设计协助并推荐合适的外部天线。如有必要,请随时联系移远通信技术支持。

天线设计要求

| 天线类型 | 要求 |

引脚天线接口 RF 同轴连接器 |

|

| PCB 天线 |

|

电气特性与可靠性

绝对最大额定值

绝对最大额定值(单位:V):

| 参数 | 最小值 | 最大值 |

|---|---|---|

| VBAT | -0.3 | 3.6 |

| 数字引脚电压 | -0.3 | 3.6 |

| ADC[1:6] 输入电压 | 0 | 3.6 |

电源额定值

模块电源额定值(单位:V)

| 参数 | 描述 | 条件 | 最小值 | 典型值 | 最大值 |

|---|---|---|---|---|---|

| VBAT | 模块电源供应 | 实际输入电压必须保持在最小值和最大值之间。 | 3.0 | 3.3 | 3.6 |

功耗

Wi-Fi 功耗

| 条件 | IVBAT | ||

|---|---|---|---|

| 2.4 GHz | 802.11b | Tx 1 Mbps @ 18 dBm | 267.11 |

| Tx 11 Mbps @ 18 dBm | 271.50 | ||

| 802.11g | Tx 6 Mbps @ 16 dBm | 246.18 | |

| Tx 54 Mbps @ 15 dBm | 245.68 | ||

| 802.11n | Tx HT20 MCS 0 @ 15 dBm | 245.40 | |

| Tx HT20 MCS 7 @ 14 dBm | 233.00 | ||

蓝牙功耗

非信令模式功耗(典型值;单位:mA)

| 条件 | IVBAT |

|---|---|

| BLE (1 Mbps) | 90.54 |

| BLE (2 Mbps) | 65.13 |

| BLE (S = 2) | 81.73 |

| BLE (S = 8) | 103.67 |

数字 I/O 特性

VBAT I/O 要求(单位:V)

| 参数 | 描述 | 最小值 | 最大值 |

|---|---|---|---|

| VIH | 高电平输入电压 | 0.7 × VBAT | VBAT |

| VIL | 低电平输入电压 | 0 | 0.3 × VBAT |

| VOH | 高电平输出电压 | 0.9 × VBAT | - |

| VOL | 低电平输出电压 | - | 0.1 × VBAT |

ESD 保护

静电自然发生,它可能损坏模块。因此,应用适当的 ESD 对策和处理方法是必要的。例如,在模块的开发、生产、组装和测试期间佩戴防静电手套;在产品设计中为 ESD 敏感接口和点添加 ESD 保护组件。

ESD 特性(单位:kV)

| 型号 | 测试结果 | 标准 |

|---|---|---|

| 人体模型 (HBM) | ±2 | ANSI/ESDA/JEDEC JS-001-2017 |

| 充电设备模型 (CDM) | ±0.5 | ANSI/ESDA/JEDEC JS-002-2018 |

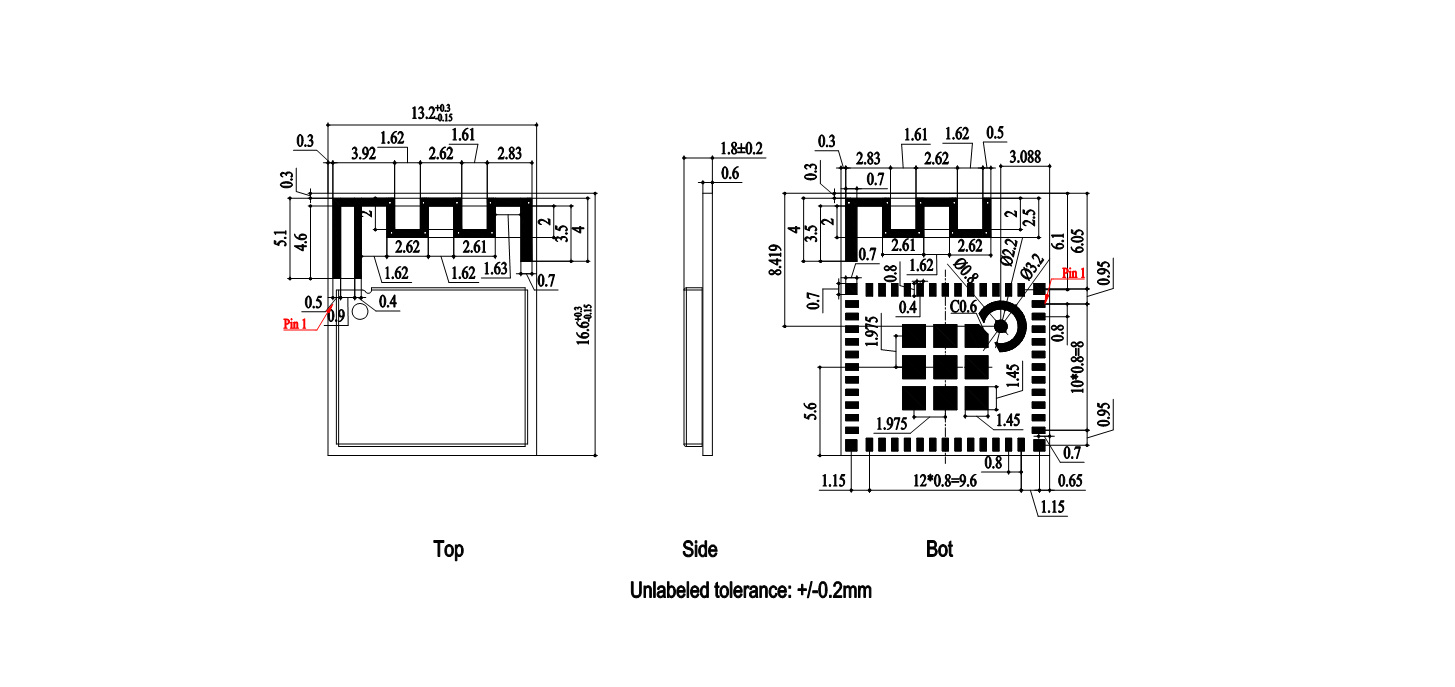

机械信息

本章描述模块的机械尺寸。所有尺寸以毫米 (mm) 为单位测量,除非另有指定,否则尺寸公差为 ±0.2 mm。

机械尺寸

模块的共面度标准:≤ 0.13 mm。

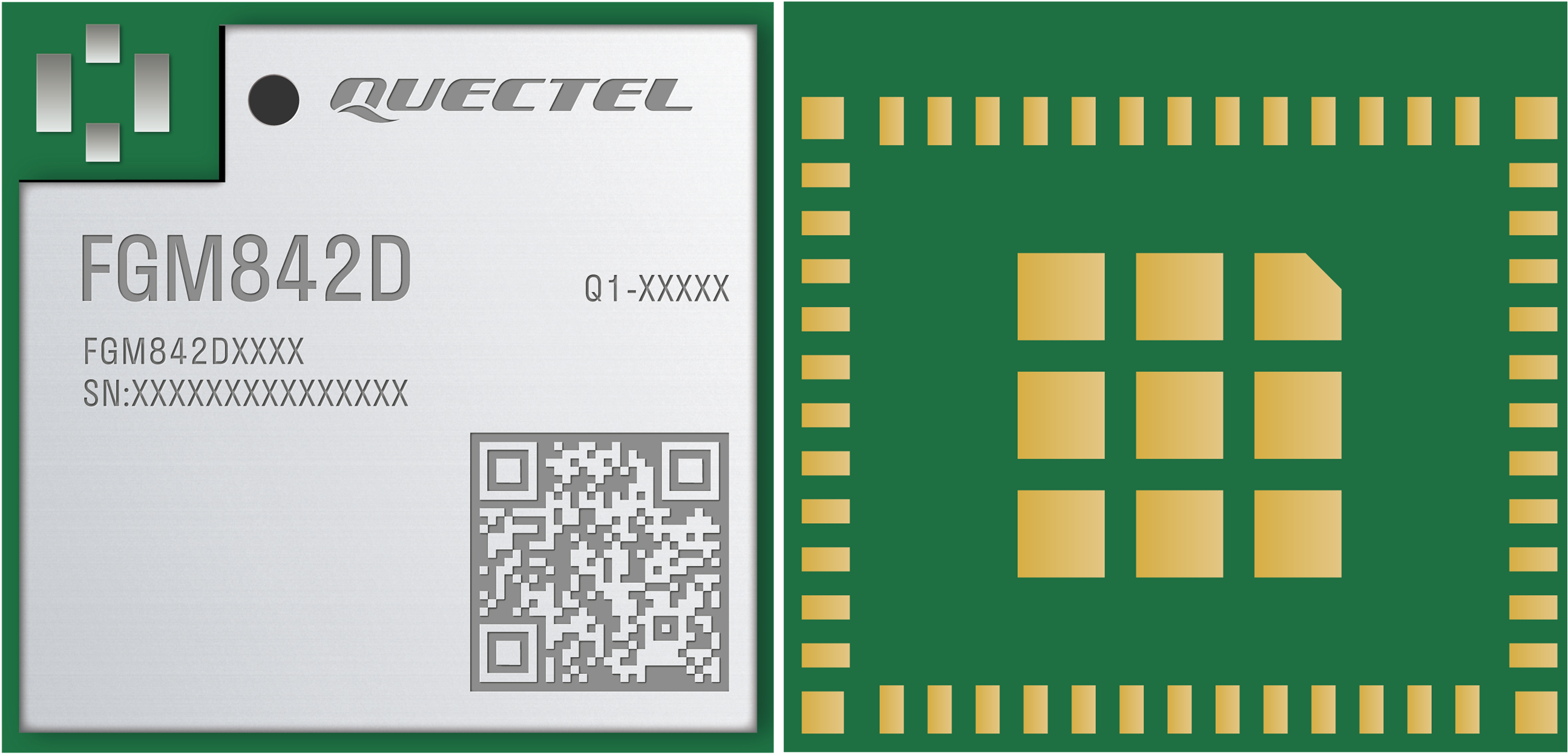

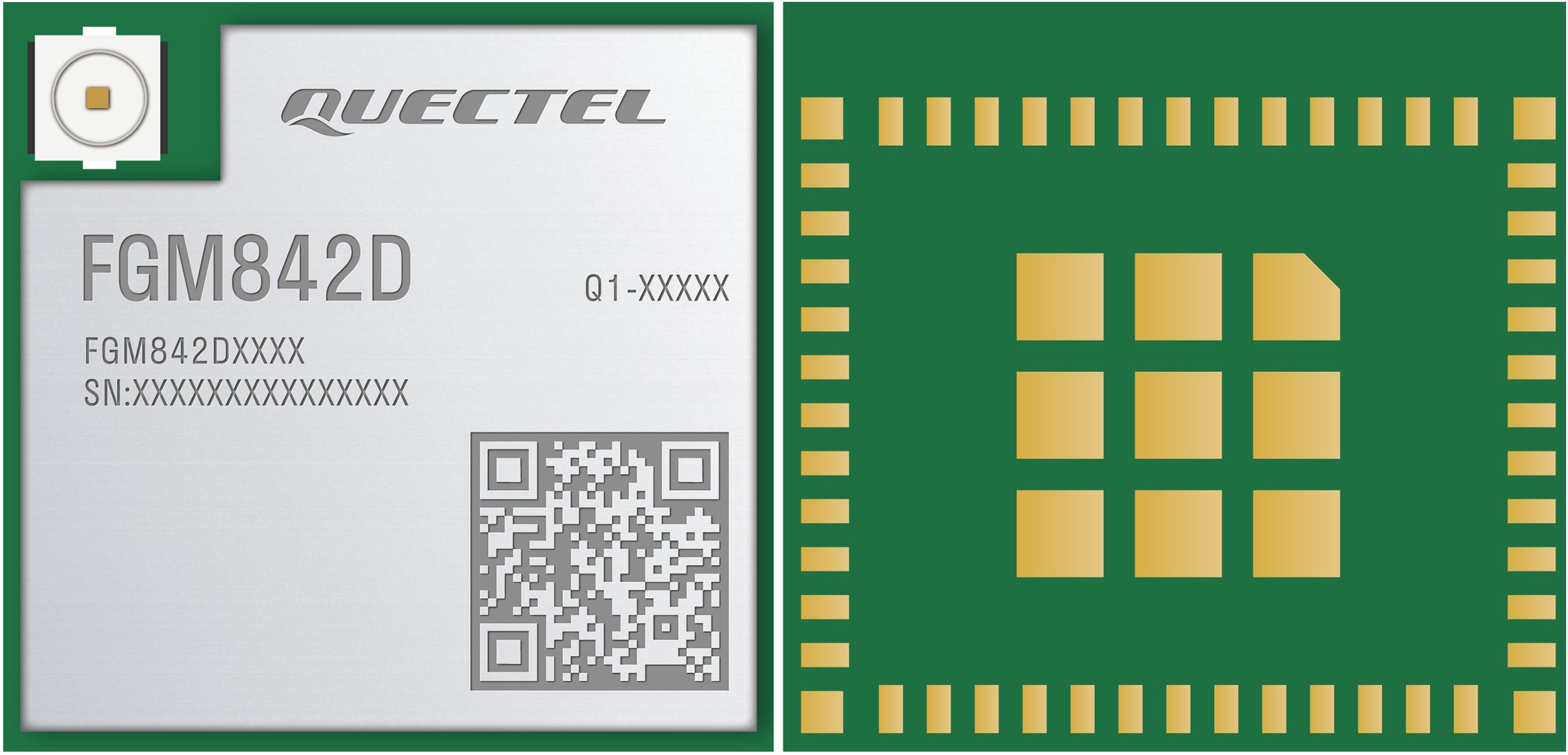

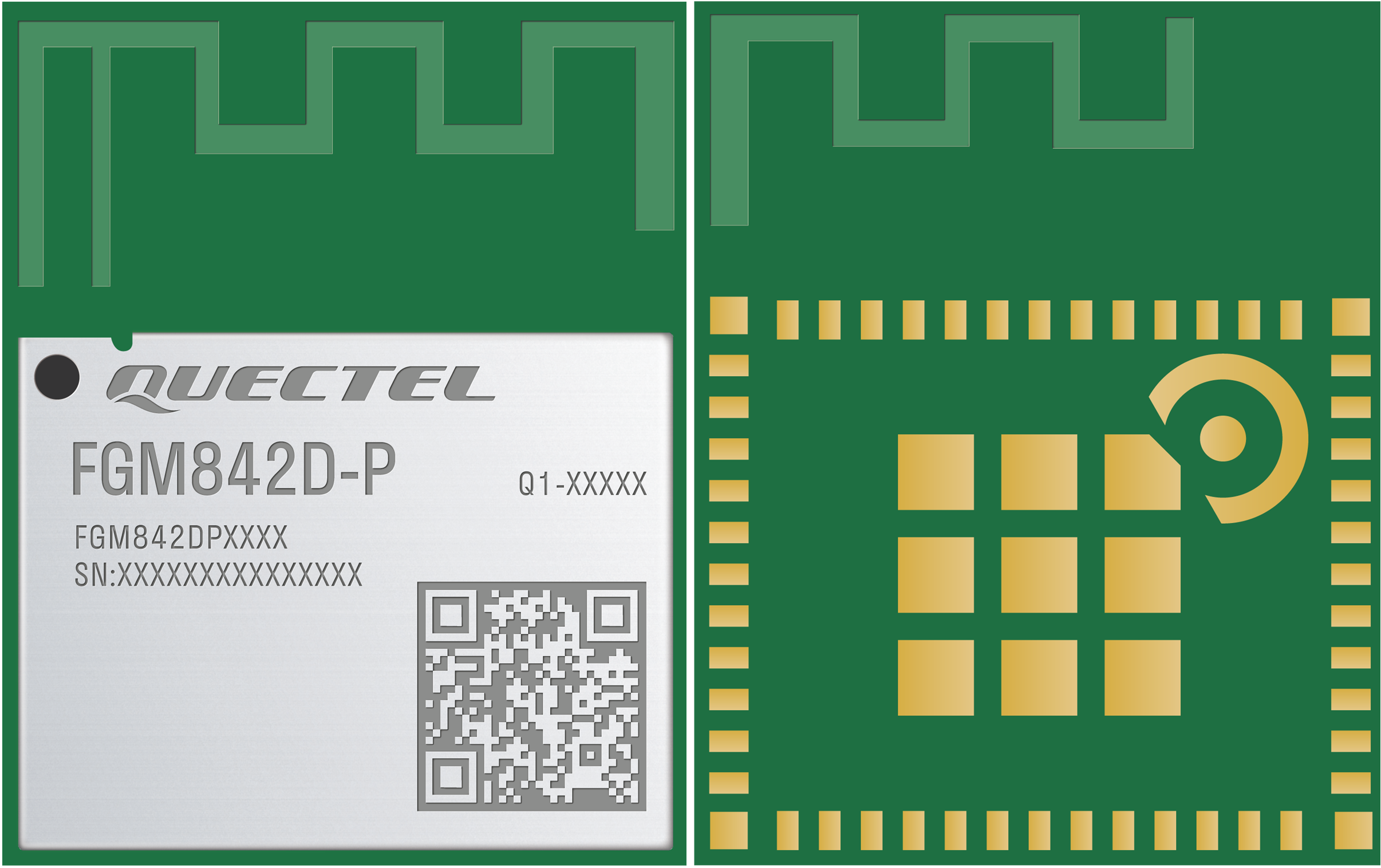

顶部和底部视图

- 上图仅供说明目的,可能与实际模块不同。有关真实外观和标签,请参考从移远通信收到的模块。

- 使用引脚天线接口 (ANT_WIFI/BT) 时,FGM842D 上不安装 RF 同轴连接器。

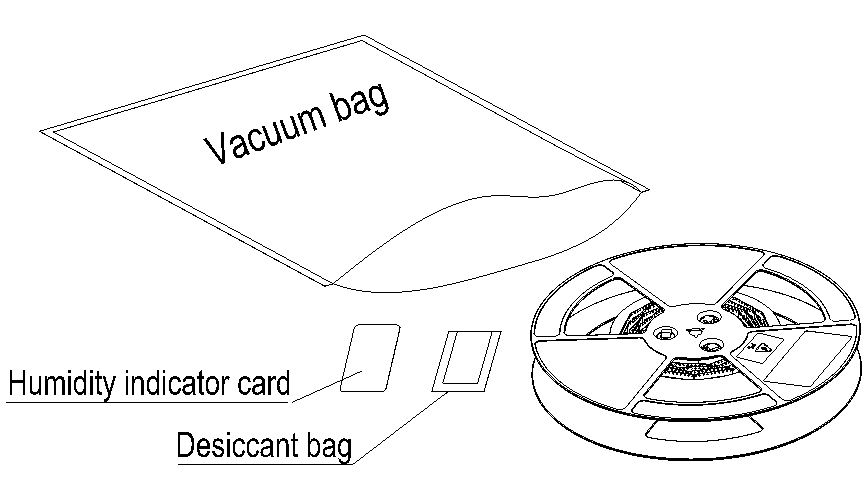

存储、制造和包装

存储条件

模块以真空密封包装提供。模块的 MSL 额定为 3。存储要求如下。

推荐存储条件:温度应为 23 ±5 °C,相对湿度应为 35–60 %。

真空密封包装中的保质期:推荐存储条件下 12 个月。

地面寿命:温度为 23 ±5 °C、相对湿度低于 60 % 的工厂中 168 小时 7。真空密封包装移除后,模块必须在 168 小时内进行回流焊接或其他高温操作。否则,模块应存储在相对湿度低于 10 % 的环境中(如干燥柜)。

在以下情况下,模块应进行预烘烤以避免 PCB 起泡、开裂和内层分离:

- 模块未存储在推荐存储条件下;

- 违反上述第三项要求;

- 真空密封包装破损,或包装已移除超过 24 小时;

- 在模块修复之前。

如需要,预烘烤应遵循以下要求:

- 模块在 120 ±5 °C 下烘烤 24 小时;

- 烘烤后,模块必须在 24 小时内焊接到 PCB,否则应放入干燥环境中,如干燥柜。

- 为避免起泡、层分离和其他焊接问题,模块暴露在空气中的时间不应延长。

- 在烘烤前,将模块从包装中取出并放在高温耐受夹具上。如果需要更短的烘烤时间,请参见 IPC/JEDEC J-STD-033 以获取烘烤程序。

- 触摸模块时,请注意 ESD 保护,例如佩戴防静电手套。

制造和焊接

将刮刀推过模板表面以将焊膏应用到 PCB 上,从而使焊膏填充模板开口并渗透到 PCB。为产生干净的模板表面,在单次通过中对刮刀施加适当力。为保证模块焊接质量,模块的模板厚度推荐为 0.15–0.18 mm。有关更多详细信息,请参见 Module-Stencil-Design-Requirements。

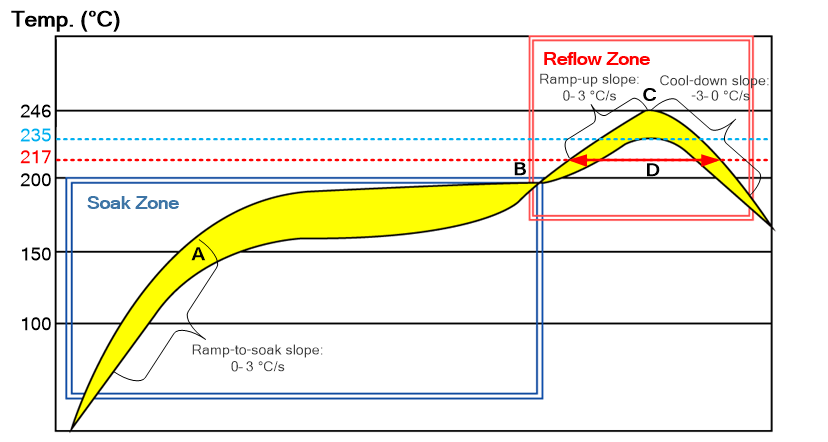

推荐的峰值回流温度应为 235–246 ºC,以 246 ºC 为绝对最大回流温度。为避免重复加热对模块造成的损坏,建议在完成 PCB 另一侧的回流焊接后才安装模块。推荐的无铅回流焊接热剖面和相关参数如下所示。

推荐热剖面参数:

| 因子 | 推荐值 |

|---|---|

| 浸泡区 | |

| 上升至浸泡斜率 | 0–3 °C/s |

| 浸泡时间(A 和 B 之间:150 °C 和 200 °C) | 70–120 s |

| 回流区 | |

| 上升斜率 | 0–3 °C/s |

| 回流时间 (D: 超过 217 °C) | 40–70 s |

| 最大温度 | 235–246 °C |

| 冷却斜率 | -3–0 °C/s |

| 回流周期 | |

| 最大回流周期 | 1 |

- 上述剖面参数要求适用于焊点的测量温度。PCB 上焊点的最高和最低点应符合上述要求。

- 在制造和焊接期间,或任何其他可能直接接触模块的过程,切勿用有机溶剂(如丙酮、乙醇、异丙醇、三氯乙烯等)擦拭模块的屏蔽罩。否则,屏蔽罩可能会生锈。

- 模块的屏蔽罩由镍铜基材料制成。经过 12 小时的中性盐雾测试,激光刻蚀在屏蔽罩上的标签信息仍清晰可辨,二进制码仍可读取,尽管可能有白锈。

- 如果模块需要保形涂层,请勿使用任何可能与 PCB 或屏蔽罩发生化学反应的涂层材料,并防止涂层材料流入模块。

- 避免使用超声波技术清洁模块,因为它可以损坏模块内的晶体。

- 避免在模块处理中使用含有汞 (Hg) 的材料,如粘合剂,即使这些材料符合 RoHS 标准且汞含量低于 1000 ppm (0.1 %)。

- 腐蚀性气体可能腐蚀模块内的电子组件,影响其可靠性和性能,并可能导致服务寿命不符合设计寿命。因此,不要在含有腐蚀性气体(如硫化氢、二氧化硫、氯气和氨)的环境中存储或使用未保护的模块。

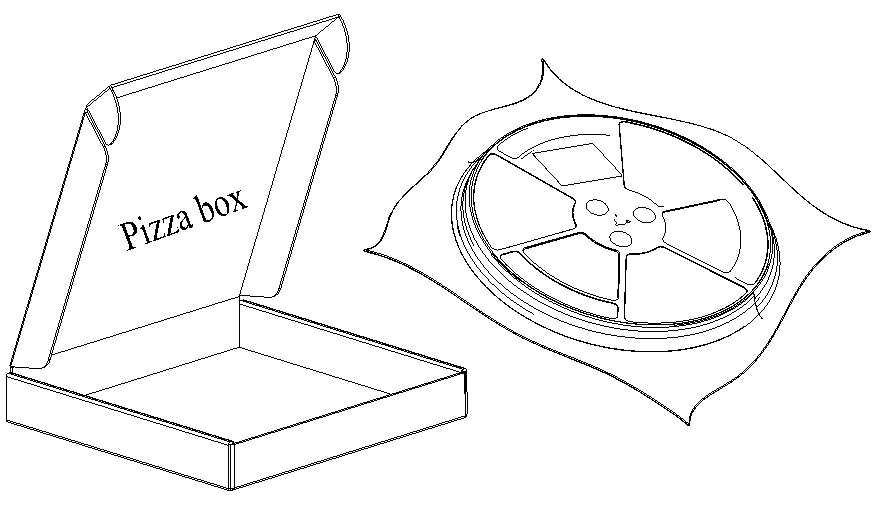

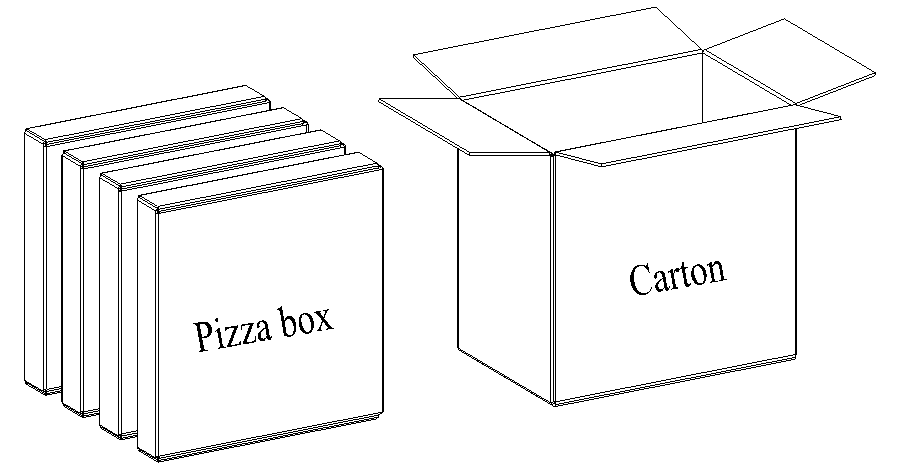

包装规格

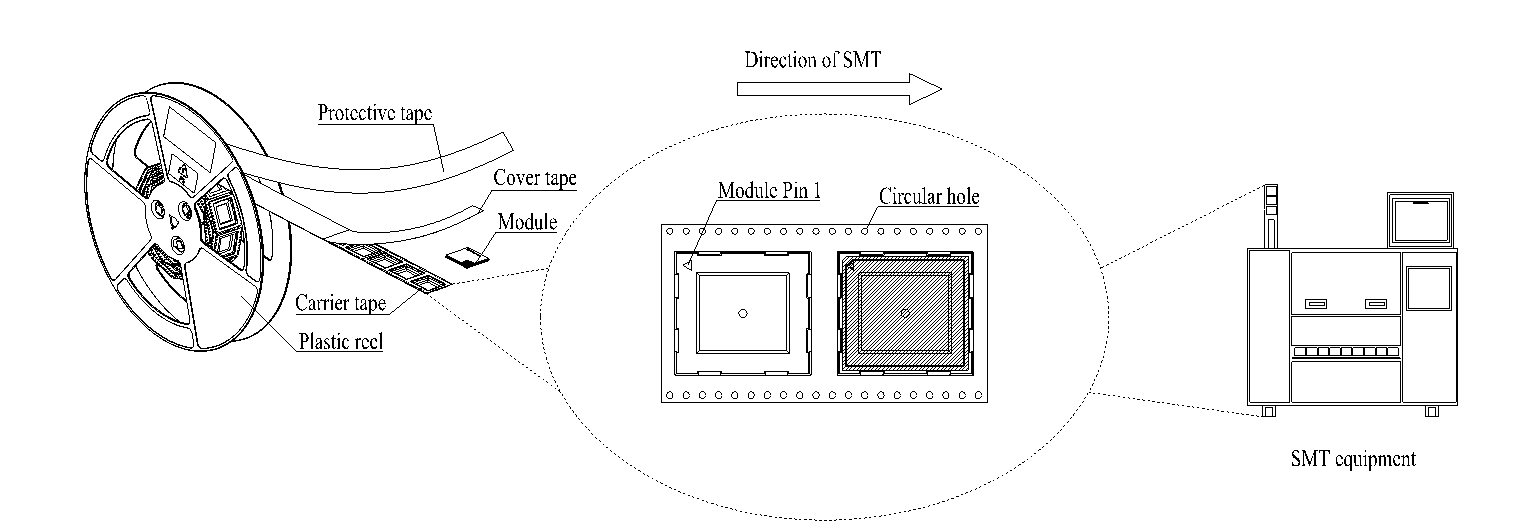

本章概述关键包装参数和过程。以下所有图仅供参考,因为交付中的实际外观和结构可能有所不同。

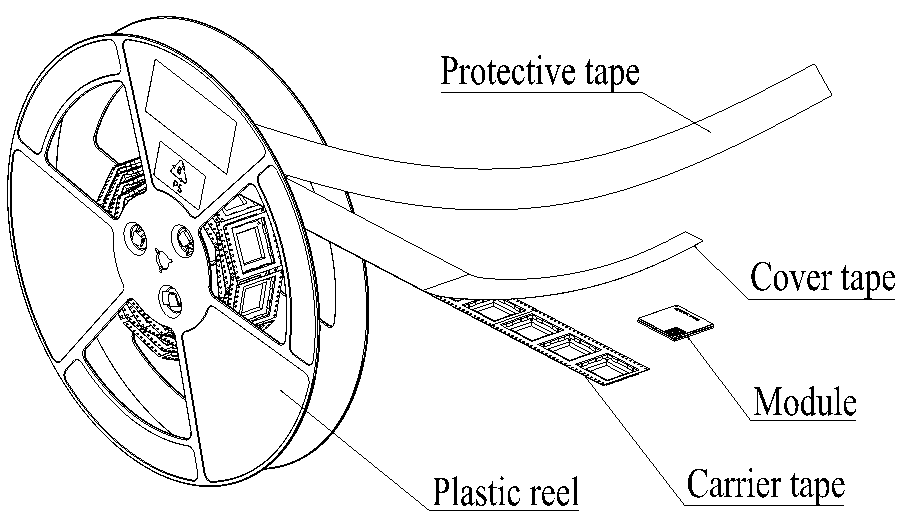

模块以载体带和卷盘包装指定在以下子章节中。

载体带

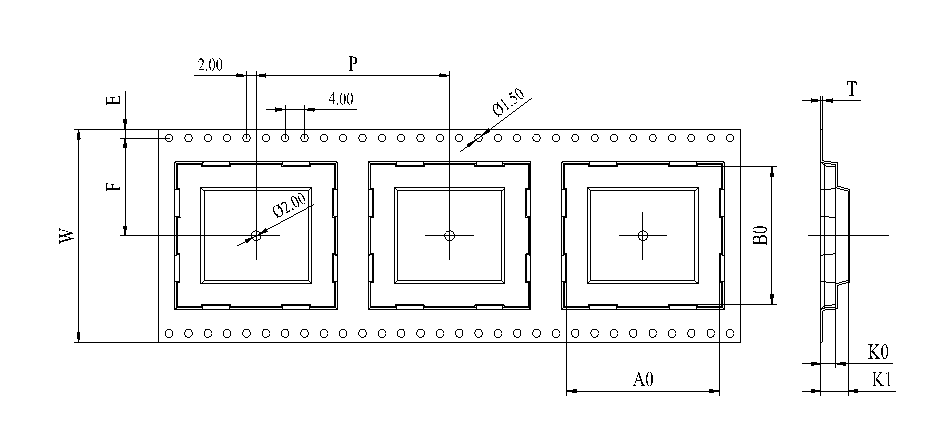

载体带尺寸如下图和表所示:

FGM842D 载体带尺寸表(单位:mm)

| W | P | T | A0 | B0 | K0 | K1 | F | E |

|---|---|---|---|---|---|---|---|---|

| 32 | 24 | 0.4 | 13.6 | 12.9 | 2.3 | 3.2 | 14.2 | 1.75 |

FGM842D-P 载体带尺寸表(单位:mm)

| W | P | T | A0 | B0 | K0 | K1 | F | E |

|---|---|---|---|---|---|---|---|---|

| 32 | 24 | 0.4 | 13.6 | 17 | 2.3 | 3.2 | 14.2 | 1.75 |

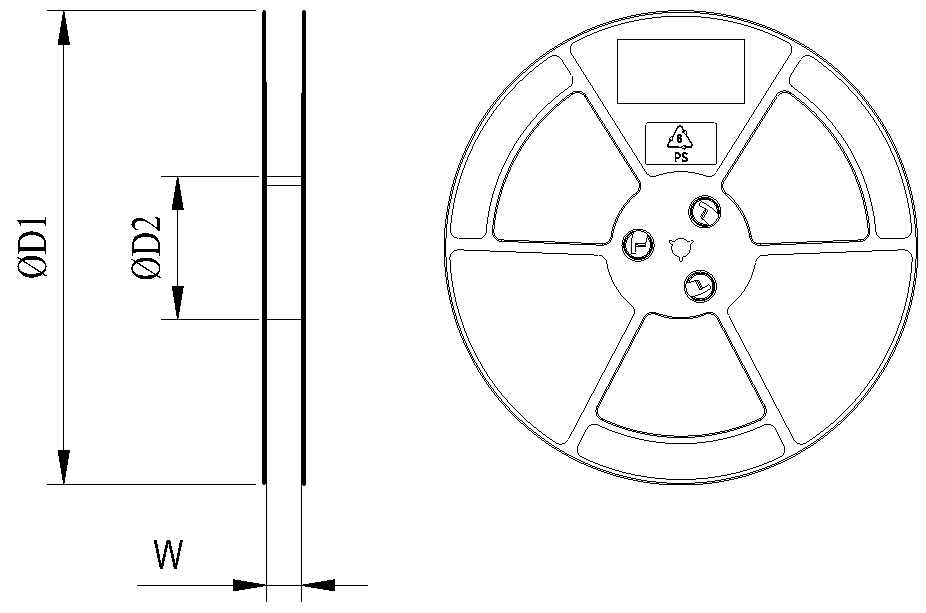

塑料卷盘

塑料卷盘尺寸如下图和表所示:

塑料卷盘尺寸表(单位:mm)

| øD1 | øD2 | W |

|---|---|---|

| 380 | 100 | 32.5 |

安装方向

中文 简体

中文 简体